## CYV15G0203TB

# Independent Clock Dual HOTLink II™ Serializer

## Features

- Second-generation HOTLink<sup>®</sup> technology

- Compliant to SMPTE 292M and SMPTE 259M video standards

- Dual-channel video serializer

- 195- to 1500-Mbps serial data signaling rate

- Simultaneous operation at different signaling rates

- · Supports half-rate and full-rate clocking

- Internal phase-locked loops (PLLs) with no external PLL components

- Redundant differential PECL-compatible serial outputs per channel

- No external bias resistors required

- Signaling-rate controlled edge-rates

- Internal source termination

- Synchronous LVTTL parallel interface

- JTAG boundary scan

- Built-In Self-Test (BIST) for at-speed link testing

- Low-power 1.4W @ 3.3V typical

- Single 3.3V supply

- Thermally enhanced BGA

- Pb-Free package option available

- 0.25µ BiCMOS technology

### **Functional Description**

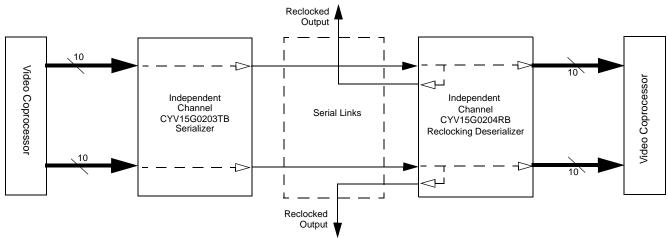

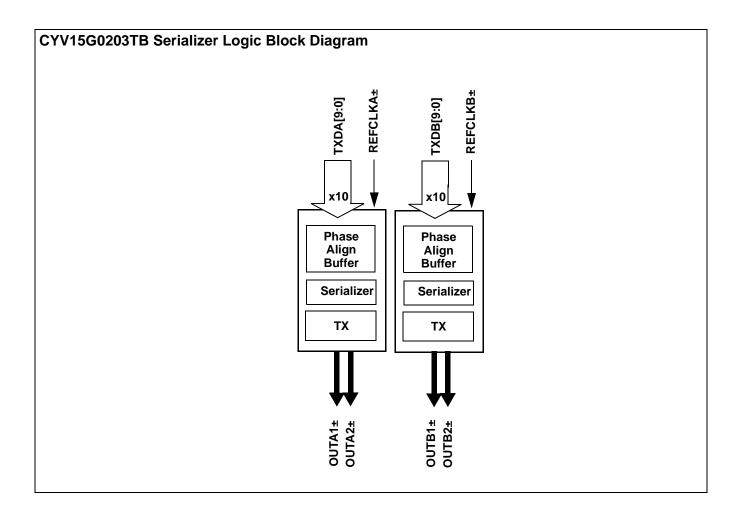

The CYV15G0203TB Independent Clock Dual HOTLink II<sup>™</sup> Serializer is a point-to-point or point-to-multipoint communications building block enabling transfer of data over a variety of high-speed serial links including SMPTE 292M and SMPTE 259M video applications. It supports signaling rates in the range of 195 to 1500 Mbps per serial link. The two channels are independent and can simultaneously operate at different rates. Each channel accepts 10-bit parallel characters in an Input Register and converts them to serial data. Figure 1 illustrates typical connections between independent video co-processors and corresponding CYV15G0203TB Serializer and CYV15G0204RB Reclocking Deserializer chips.

The CYV15G0203TB satisfies the SMPTE-259M and SMPTE-292M compliance as per SMPTE EG34-1999 Pathological Test Requirements.

As a second-generation HOTLink device, the CYV15G0203TB extends the HOTLink family with enhanced levels of integration and faster data rates, while maintaining serial-link compatibility (data, and BIST) with other HOTLink devices. Each channel of the CYV15G0203TB Dual HOTLink II device accepts scrambled 10-bit transmission characters. These characters are serialized and output from dual Positive ECL (PECL) compatible differential transmission-line drivers at a bit-rate of either 10- or 20-times the input reference clock for that channel.

Each channel contains an independent BIST pattern generator. This BIST hardware allows at-speed testing of the high-speed serial data paths in each transmit section of this device, each receive section of a connected HOTLink II device, and across the interconnecting links.

The CYV15G0203TB is ideal for SMPTE applications where different data rates and serial interface standards are necessary for each channel. Some applications include multi-format routers, switchers, format converters, and cameras.

#### Figure 1. HOTLink II<sup>™</sup> System Connections

Cypress Semiconductor Corporation Document #: 38-02105 Rev. \*C 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Revised May 2, 2007

## Pin Configuration (Top View)<sup>[1]</sup>

|   | 1               | 2               | 3               | 4               | 5               | 6               | 7          | 8   | 9           | 10          | 11           | 12          | 13  | 14          | 15          | 16              | 17              | 18              | 19              | 20              |

|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------|-----|-------------|-------------|--------------|-------------|-----|-------------|-------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| A | NC              | NC              | NC              | NC              | V <sub>CC</sub> | NC              | OUT<br>B1– | GND | GND         | OUT<br>B2–  | GND          | OUT<br>A1–  | GND | GND         | OUT<br>A2–  | V <sub>CC</sub> | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              |

| В | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> | V <sub>CC</sub> | OUT<br>B1+ | GND | NC          | OUT<br>B2+  | NC           | OUT<br>A1+  | GND | NC          | OUT<br>A2+  | V <sub>CC</sub> | NC              | NC              | NC              | NC              |

| С | TDI             | TMS             | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | NC              | NC         | GND | NC          | NC          | DATA<br>[2]  | DATA<br>[0] | GND | NC          | SPD<br>SELB | V <sub>CC</sub> | NC              | TRST            | GND             | TDO             |

| D | TCLK            | RESET           | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | NC         | GND | GND         | DATA<br>[3] | DATA<br>[1]  | GND         | GND | GND         | NC          | V <sub>CC</sub> | NC              | NC              | SCAN<br>EN2     | TMEN3           |

| Е | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |                 |                 |            | I   | 1           |             |              | 1           | 1   |             |             |                 | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |

| F | NC              | NC              | V <sub>CC</sub> | NC              |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | NC              | NC              |

| G | GND             | WREN            | GND             | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | SPD<br>SELA     | NC              |

| Н | GND             | GND             | GND             | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | GND             | GND             | GND             | GND             |

| J | GND             | GND             | GND             | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | NC              | NC              |

| К | NC              | NC              | GND             | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | NC              | NC              |

| L | NC              | NC              | NC              | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | NC              | GND             |

| Μ | NC              | NC              | NC              | NC              |                 |                 |            |     |             |             |              |             |     |             |             |                 | NC              | NC              | NC              | GND             |

| N | GND             | GND             | GND             | GND             |                 |                 |            |     |             |             |              |             |     |             |             |                 | GND             | GND             | GND             | GND             |

| Ρ | NC              | NC              | NC              | NC              |                 |                 |            |     |             |             |              |             |     |             |             |                 | GND             | GND             | GND             | GND             |

| R | NC              | NC              | NC              | NC              |                 |                 |            |     |             |             |              |             |     |             |             |                 | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |

| Т | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |                 |                 |            |     |             |             |              |             |     |             |             |                 | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |

| U | TX<br>DB[0]     | TX<br>DB[1]     | TX<br>DB[2]     | TX<br>DB[9]     | V <sub>CC</sub> | NC              | NC         | GND | TX<br>DA[9] | ADDR<br>[0] | REF<br>CLKB– | TX<br>DA[1] | GND | TX<br>DA[4] | TX<br>DA[8] | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              | NC              |

| V | TX<br>DB[3]     | TX<br>DB[4]     | TX<br>DB[8]     | NC              | V <sub>CC</sub> | NC              | NC         | GND | NC          | GND         | REF<br>CLKB+ | TX<br>CLKOA | GND | TX<br>DA[3] | TX<br>DA[7] | V <sub>CC</sub> | NC              | NC              | NC              | NC              |

| W | TX<br>DB[5]     | TX<br>DB[7]     | NC              | NC              | V <sub>CC</sub> | NC              | NC         | GND | ADDR<br>[2] | ADDR<br>[1] | NC           | TX<br>ERRA  | GND | TX<br>DA[2] | TX<br>DA[6] | V <sub>CC</sub> | NC              | REF<br>CLKA+    | NC              | NC              |

| Y | TX<br>DB[6]     | TX<br>CLKB      | NC              | NC              | V <sub>CC</sub> | NC              | NC         | GND | TX<br>CLKOB | NC          | TX<br>CLKA   | NC          | GND | TX<br>DA[0] | TX<br>DA[5] | V <sub>CC</sub> | TX<br>ERRB      | REF<br>CLKA-    | NC              | NC              |

Note 1. NC = Do not connect.

## Pin Configuration (Bottom View)<sup>[1]</sup>

|   | 20              | 19              | 18              | 17              | 16              | 15          | 14          | 13  | 12          | 11           | 10          | 9           | 8   | 7          | 6               | 5               | 4               | 3               | 2               | 1               |

|---|-----------------|-----------------|-----------------|-----------------|-----------------|-------------|-------------|-----|-------------|--------------|-------------|-------------|-----|------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| А | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> | V <sub>CC</sub> | OUT<br>A2–  | GND         | GND | OUT<br>A1–  | GND          | OUT<br>B2–  | GND         | GND | OUT<br>B1– | NC              | V <sub>CC</sub> | NC              | NC              | NC              | NC              |

| В | NC              | NC              | NC              | NC              | V <sub>CC</sub> | OUT<br>A2+  | NC          | GND | OUT<br>A1+  | NC           | OUT<br>B2+  | NC          | GND | OUT<br>B1+ | V <sub>CC</sub> | V <sub>CC</sub> | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> |

| С | TDO             | GND             | TRST            | NC              | V <sub>CC</sub> | SPD<br>SELB | NC          | GND | DATA<br>[0] | DATA<br>[2]  | NC          | NC          | GND | NC         | NC              | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | TMS             | TDI             |

| D | TMEN3           | SCAN<br>EN2     | NC              | NC              | V <sub>CC</sub> | NC          | GND         | GND | GND         | DATA<br>[1]  | DATA<br>[3] | GND         | GND | NC         | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | RESET           | TCLK            |

| Е | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |                 | I           |             |     | I           |              | I           | I           | 1   |            |                 |                 | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |

| F | NC              | NC              | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | NC              | V <sub>CC</sub> | NC              | NC              |

| G | NC              | SPD<br>SELA     | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | GND             | WREN            | GND             |

| н | GND             | GND             | GND             | GND             |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | GND             | GND             | GND             |

| J | NC              | NC              | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | GND             | GND             | GND             |

| к | NC              | NC              | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | GND             | NC              | NC              |

| L | GND             | NC              | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | NC              | NC              | NC              |

| М | GND             | NC              | NC              | NC              |                 |             |             |     |             |              |             |             |     |            |                 |                 | NC              | NC              | NC              | NC              |

| N | GND             | GND             | GND             | GND             |                 |             |             |     |             |              |             |             |     |            |                 |                 | GND             | GND             | GND             | GND             |

| Р | GND             | GND             | GND             | GND             |                 |             |             |     |             |              |             |             |     |            |                 |                 | NC              | NC              | NC              | NC              |

| R | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |                 |             |             |     |             |              |             |             |     |            |                 |                 | NC              | NC              | NC              | NC              |

| т | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |                 |             |             |     |             |              |             |             |     |            |                 |                 | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> |

| U | NC              | NC              | V <sub>CC</sub> | NC              | V <sub>CC</sub> | TX<br>DA[8] | TX<br>DA[4] | GND | TX<br>DA[1] | REF<br>CLKB- | ADDR<br>[0] | TX<br>DA[9] | GND | NC         | NC              | V <sub>CC</sub> | TX<br>DB[9]     | TX<br>DB[2]     | TX<br>DB[1]     | TX<br>DB[0]     |

| V | NC              | NC              | NC              | NC              | V <sub>CC</sub> | TX<br>DA[7] | TX<br>DA[3] | GND | TX<br>CLKOA | REF<br>CLKB+ | GND         | NC          | GND | NC         | NC              | V <sub>CC</sub> | NC              | TX<br>DB[8]     | TX<br>DB[4]     | TX<br>DB[3]     |

| W | NC              | NC              | REF<br>CLKA+    | NC              | V <sub>CC</sub> | TX<br>DA[6] | TX<br>DA[2] | GND | TX<br>ERRA  | NC           | ADDR<br>[1] | ADDR<br>[2] | GND | NC         | NC              | V <sub>CC</sub> | NC              | NC              | TX<br>DB[7]     | TX<br>DB[5]     |

| Y | NC              | NC              | REF<br>CLKA–    | TX<br>ERRB      | V <sub>CC</sub> | TX<br>DA[5] | TX<br>DA[0] | GND | NC          | TX<br>CLKA   | NC          | TX<br>CLKOB | GND | NC         | NC              | V <sub>CC</sub> | NC              | NC              | TX<br>CLKB      | TX<br>DB[6]     |

## **Pin Definitions** CYV15G0203TB Dual HOTLink II Serializer

| Name                   | I/O Characteristics                                                                                                                                                       | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Path          | h Data and Status Signals                                                                                                                                                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXDA[9:0]<br>TXDB[9:0] | LVTTL Input,<br>synchronous,<br>sampled by the<br>associated<br>TXCLKx↑ or<br>REFCLKx <sup>↑[2]</sup>                                                                     | <b>Transmit Data Inputs</b> . TXDx[9:0] data inputs are captured on the rising edge of the transmit interface clock. The transmit interface clock is selected by the TXCKSELx latch via the device configuration interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TXERRA<br>TXERRB       | LVTTL Output,<br>synchronous to<br>REFCLKx <sup>1[3]</sup> ,<br>asynchronous to<br>transmit channel<br>enable / disable,<br>asynchronous to loss<br>or return of REFCLKx± | <b>Transmit Path Error</b> . TXERRx is asserted HIGH to indicate detection of a transmit Phase-Align Buffer underflow or overflow. If an underflow or overflow condition is detected, TXERRx, for the channel in error, is asserted HIGH and remains asserted until the transmit Phase-Align Buffer is re-centered with the PABRSTx latch via the device configuration interface. When TXBISTx = 0, the BIST progress is presented on the associated TXERRx output. The TXERRx signal pulses HIGH for one transmit-character clock period to indicate a pass through the BIST sequence once every 511 character times.                                                                                                                                                                                                                                                                           |

|                        |                                                                                                                                                                           | <ul> <li>TXERRx is also asserted HIGH, when any of the following conditions is true:</li> <li>The TXPLL for the associated channel is powered down. This occurs when OE2x and OE1x for a given channel are both disabled by setting OE2x = 0 and OE1x = 0.</li> <li>The absence of the REFCLKx± signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Transmit Patl          | h Clock Signals                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REFCLKA±<br>REFCLKB±   | Differential LVPECL or<br>single-ended<br>LVTTL input clock                                                                                                               | <b>Reference Clock.</b> REFCLKx± clock inputs are used as the timing references for the associated transmit PLL. These input clocks may also be selected to clock the transmit parallel interface. When driven by a single-ended LVCMOS or LVTTL clock source, connect the clock source to either the true or complement REFCLKx input, and leave the alternate REFCLKx input open (floating). When driven by an LVPECL clock source, the clock must be a differential clock, using both inputs.                                                                                                                                                                                                                                                                                                                                                                                                 |

| TXCLKA<br>TXCLKB       | LVTTL Clock Input,<br>internal pull-down                                                                                                                                  | <b>Transmit Path Input Clock</b> . When configuration latch TXCKSELx = 0, the associated TXCLKx input is selected as the character-rate input clock for the TXDB[9:0] input. In this mode, the TXCLKx input must be frequency-coherent to its associated TXCLKOx output clock, but may be offset in phase by any amount. Once initialized, TXCLKx is allowed to drift in phase as much as ±180 degrees. If the input phase of TXCLKx drifts beyond the handling capacity of the Phase Align Buffer, TXERRx is asserted to indicate the loss of data, and remains asserted until the Phase Align Buffer is initialized. The phase of the TXCLKx input clock relative to its associated REFCLKx± is initialized when the configuration latch PABRSTx is written as 0. When the associated TXERRx is deasserted, the Phase Align Buffer is initialized and input characters are correctly captured. |

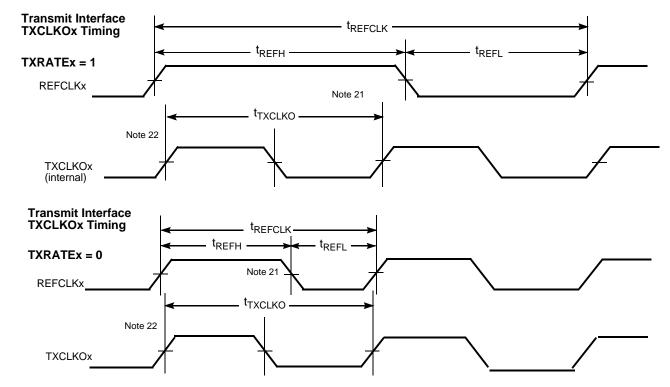

| TXCLKOA<br>TXCLKOB     | LVTTL Output                                                                                                                                                              | <b>Transmit Clock Output</b> . TXCLKOx output clock is synthesized by each channel's transmit PLL and operates synchronous to the internal transmit character clock. TXCLKOx operates at either the same frequency as REFCLKx $\pm$ (TXRATEx = 0), or at twice the frequency of REFCLKx $\pm$ (TXRATEx = 1). The transmit clock outputs have no fixed phase relationship to REFCLKx $\pm$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Device Contr           | ol Signals                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET                  | LVTTL Input,<br>asynchronous,<br>internal pull-up                                                                                                                         | Asynchronous Device Reset. RESET initializes all state machines, counters, and configuration latches in the device to a known state. RESET must be asserted LOW for a minimum pulse width. When the reset is removed, all state machines, counters and configuration latches are at an initial state. As per the JTAG specifications the device RESET cannot reset the JTAG controller. Therefore, the JTAG controller has to be reset separately. Refer to "JTAG Support" on page 10 for the methods to reset the JTAG state machine. See Table 2 on page 10 for the initialize values of the device configuration latches.                                                                                                                                                                                                                                                                     |

Notes

2. When REFCLKx± is configured for half-rate operation, these inputs are sampled relative to both the rising and falling edges of the associated REFCLKx±.

3. When REFCLKx± is configured for half-rate operation, these outputs are presented relative to both the rising and falling edges of the associated REFCLKx±.

## Pin Definitions (continued) CYV15G0203TB Dual HOTLink II Serializer

| Name               | I/O Characteristics                                   | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPDSELA<br>SPDSELB | 3-Level Select <sup>[4]</sup><br>static control input | Serial Rate Select. The SPDSELx inputs specify the operating signaling-rate range of each channel's PLL.                                                                                                                                                                                                                                                                                                                                                              |

|                    |                                                       | LOW = 195–400 MBd                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                                                       | MID = 400–800 MBd                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                                                       | HIGH = 800–1500 MBd.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | ration and Control Bus                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

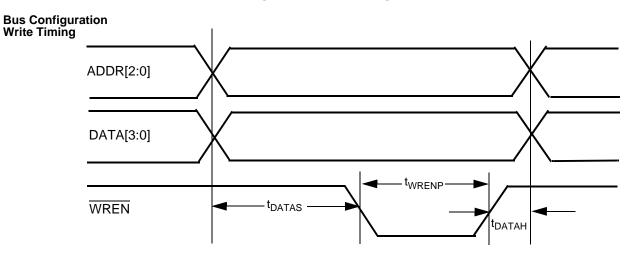

| WREN               | LVTTL input,<br>asynchronous,<br>internal pull-up     | <b>Control Write Enable</b> . The WREN input writes the values of the DATA[3:0] bus into the latch specified by the address location on the ADDR[2:0] bus. <sup>[5]</sup>                                                                                                                                                                                                                                                                                             |

| ADDR[2:0]          | LVTTL input<br>asynchronous,<br>internal pull-up      | <b>Control Addressing Bus.</b> The ADDR[2:0] bus is the input address bus used to configure the device. The WREN input writes the values of the DATA[3:0] bus into the latch specified by the address location on the ADDR[2:0] bus. <sup>[5]</sup> Table 2 on page 10 lists the configuration latches within the device, and the initialization value of the latches upon the assertion of RESET. Table 3 on page 11 shows how the latches are mapped in the device. |

| DATA[3:0]          | LVTTL input<br>asynchronous,<br>internal pull-up      | <b>Control Data Bus.</b> The DATA[3:0] bus is the input data bus used to configure the device. The WREN input writes the values of the DATA[3:0] bus into the latch specified by address location on the ADDR[2:0] bus. <sup>[5]</sup> Table 2 on page 10 lists the configuration latches within the device, and the initialization value of the latches upon the assertion of RESET. Table 3 on page 11 shows how the latches are mapped in the device.              |

| Internal Device    | <b>Configuration Latches</b>                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TXCKSEL[AB]        | Internal Latch <sup>[6]</sup>                         | Transmit Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXRATE[AB]         | Internal Latch <sup>[6]</sup>                         | Transmit PLL Clock Rate Select.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TXBIST[AB]         | Internal Latch <sup>[6]</sup>                         | Transmit Bist Disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OE2[AB]            | Internal Latch <sup>[6]</sup>                         | Differential Serial Output Driver 2 Enable.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OE1[AB]            | Internal Latch <sup>[6]</sup>                         | Differential Serial Output Driver 1 Enable.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PABRST[AB]         | Internal Latch <sup>[6]</sup>                         | Transmit Clock Phase Alignment Buffer Reset.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Factory Test Mo    | des                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SCANEN2            | LVTTL input,<br>internal pull-down                    | <b>Factory Test 2.</b> SCANEN2 input is for factory testing only. This input may be left as a NO CONNECT, or GND only.                                                                                                                                                                                                                                                                                                                                                |

| TMEN3              | LVTTL input,<br>internal pull-down                    | <b>Factory Test 3</b> . TMEN3 input is for factory testing only. This input may be left as a NO CONNECT, or GND only.                                                                                                                                                                                                                                                                                                                                                 |

| Analog I/O         |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OUTA1±<br>OUTB1±   | CML Differential<br>Output                            | <b>Primary Differential Serial Data Output</b> . The OUTx1± PECL-compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines or standard fiber-optic transmitter modules, and must be AC-coupled for PECL-compatible connections.                                                                                                                                                                                                  |

| OUTA2±<br>OUTB2±   | CML Differential<br>Output                            | <b>Secondary Differential Serial Data Output</b> . The OUTx2±PECL-compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines or standard fiber-optic transmitter modules, and must be AC-coupled for PECL-compatible connections.                                                                                                                                                                                                 |

#### Notes

<sup>3-</sup> Level Select inputs are used for static configuration. These are ternary inputs that make use of logic levels of LOW, MID, and HIGH. The LOW level is usually implemented by direct connection to V<sub>SS</sub> (ground). The HIGH level is usually implemented by direct connection to V<sub>CC</sub> (power). The MID level is usually implemented by not connecting the input (left floating), which allows it to self bias to the proper level.

See "Device Configuration and Control Interface" on page 9 for detailed information on the operation of the Configuration Interface.

See "Device Configuration and Control Interface" on page 9 for detailed information on the internal latches.

#### Pin Definitions (continued) CYV15G0203TB Dual HOTLink II Serializer

| Name            | I/O Characteristics                | Signal Description                                                                                                                                       |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Interface  |                                    |                                                                                                                                                          |

| TMS             | LVTTL Input,<br>internal pull-up   | <b>Test Mode Select</b> . Used to control access to the JTAG Test Modes. If maintained high for $\geq$ 5 TCLK cycles, the JTAG test controller is reset. |

| TCLK            | LVTTL Input,<br>internal pull-down | JTAG Test Clock.                                                                                                                                         |

| TDO             | 3-State LVTTL Output               | Test Data Out. JTAG data output buffer. High-Z while JTAG test mode is not selected.                                                                     |

| TDI             | LVTTL Input,<br>internal pull-up   | Test Data In. JTAG data input port.                                                                                                                      |

| TRST            | LVTTL Input,<br>internal pull-up   | <b>JTAG reset signal</b> . When asserted (LOW), this input asynchronously resets the JTAG test access port controller.                                   |

| Power           |                                    |                                                                                                                                                          |

| V <sub>CC</sub> |                                    | +3.3V Power.                                                                                                                                             |

| GND             |                                    | Signal and Power Ground for all internal circuits.                                                                                                       |

#### CYV15G0203TB HOTLink II Operation

The CYV15G0203TB is a highly configurable, independent clocking, dual-channel serializer, designed to support reliable transfer of large quantities of digital video data, using high-speed serial links from multiple sources to multiple destinations. This device supports two 10-bit channels.

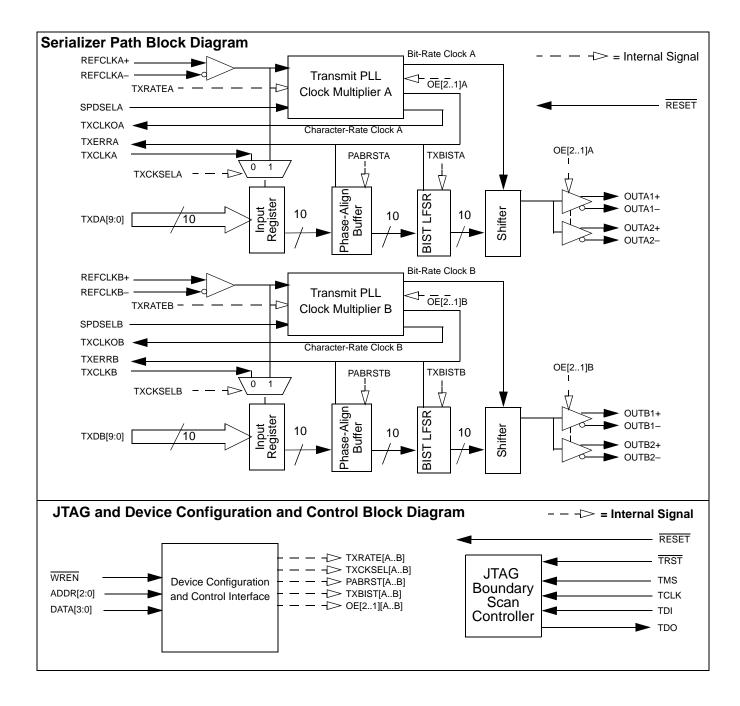

### CYV15G0203TB Transmit Data Path

#### **Input Register**

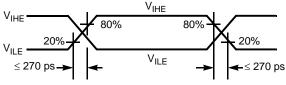

The parallel input bus TXDx[9:0] can be clocked in using TXCLKx (TXCKSELx = 0) or REFCLKx (TXCKSELx = 1).

#### **Phase-Align Buffer**

Data from each Input Register is passed to the associated Phase-Align Buffer, when the TXDx[9:0] input registers are clocked using TXCLKx (TXCKSELx = 0 and TXRATEx = 0). When the TXDx[9:0] input registers are clocked using REFCLKx $\pm$  (TXCKSELx = 1) and REFCLKx $\pm$  is a full-rate clock, the associated Phase Alignment Buffer in the transmit path is bypassed. These buffers are used to absorb clock phase differences between the TXCLKx input clock and the internal character clock for that channel.

Once initialized, TXCLKx is allowed to drift in phase as much as ±180 degrees. If the input phase of TXCLKx drifts beyond the handling capacity of the Phase Align Buffer, TXERRx is asserted to indicate the loss of data, and remains asserted until the Phase Align Buffer is initialized. The phase of the TXCLKx relative to its associated internal character rate clock is initialized when the configuration latch PABRSTx is written as 0. When the associated TXERRx is deasserted, the Phase Align Buffer is initialized and input characters are correctly captured.

If the phase offset, between the initialized location of the input clock and REFCLKx, exceeds the skew handling capabilities of the Phase-Align Buffer, an error is reported on that channel's TXERRx output. This output indicates an error continuously until the Phase-Align Buffer for that channel is reset. While the error remains active, the transmitter for that channel outputs a continuous "1001111000" character (LSB first) to indicate to the remote receiver that an error condition is present in the link.

#### **Transmit BIST**

Each channel contains an internal pattern generator that can be used to validate both the link and device operation. These generators are enabled by the associated TXBISTx latch via the device configuration interface. When enabled, a register in the associated channel becomes a signature pattern generator by logically converting to a Linear Feedback Shift Register (LFSR). This LFSR generates a 511-character sequence. This provides a predictable yet pseudo-random sequence that can be matched to an identical LFSR in the attached Receiver(s).

A device reset (RESET sampled LOW) presets the BIST Enable Latches to disable BIST on both channels.

All data present at the associated TXDx[9:0] inputs are ignored when BIST is active on that channel.

#### **Transmit PLL Clock Multiplier**

Each Transmit PLL Clock Multiplier accepts a character-rate or half-character-rate external clock at the associated REFCLKx± input, and that clock is multiplied by 10 or 20 (as selected by TXRATEx) to generate a bit-rate clock for use by the transmit shifter. It also provides a character-rate clock used by the transmit paths, and outputs this character rate clock as TXCLKOx.

Each clock multiplier PLL can accept a REFCLKx $\pm$  input between 19.5 MHz and 150 MHz, however, this clock range is limited by the operating mode of the CYV15G0203TB clock multiplier (TXRATEx) and by the level on the associated SPDSELx input.

SPDSELx are 3-level select<sup>[4]</sup> inputs that select one of three operating ranges for the serial data outputs and inputs of the associated channel. The serial signaling-rate and allowable range of REFCLKx± frequencies are listed in Table 1 on page 9.

#### **Table 1. Operating Speed Settings**

| SPDSELx    | TXRATEx | REFCLKx±<br>Frequency<br>(MHz) | Signaling<br>Rate (Mbps) |

|------------|---------|--------------------------------|--------------------------|

| LOW        | 1       | reserved                       | 195–400                  |

|            | 0       | 19.5–40                        |                          |

| MID (Open) | 1       | 20–40                          | 400-800                  |

|            | 0       | 40–80                          |                          |

| HIGH       | 1       | 40–75                          | 800–1500                 |

|            | 0       | 80–150                         |                          |

The REFCLKx± inputs are differential inputs with each input internally biased to 1.4V. If the REFCLKx+ input is connected to a TTL, LVTTL, or LVCMOS clock source, the input signal is recognized when it passes through the internally biased reference point. When driven by a single-ended TTL, LVTTL, or LVCMOS clock source, connect the clock source to either the true or complement REFCLKx input, and leave the alternate REFCLKx input open (floating).

When both the REFCLKx+ and REFCLKx- inputs are connected, the clock source must be a differential clock. This can either be a differential LVPECL clock that is DC-or AC-coupled or a differential LVTTL or LVCMOS clock.

By connecting the REFCLKx– input to an external voltage source, it is possible to adjust the reference point of the REFCLKx+ input for alternate logic levels. When doing so, it is necessary to ensure that the input differential crossing point remains within the parametric range supported by the input.

#### **Serial Output Drivers**

The serial output interface drivers use differential Current Mode Logic (CML) drivers to provide source-matched drivers for  $50\Omega$  transmission lines. These drivers accept data from the Transmit Shifter, which shifts the data out LSB first. These drivers have signal swings equivalent to that of standard PECL drivers, and are capable of driving AC-coupled optical modules or transmission lines.

#### Transmit Channels Enabled

Each driver can be enabled or disabled separately via the device configuration interface.

When a driver is disabled via the configuration interface, it is internally powered down to reduce device power. If both serial drivers for a channel are in this disabled state, the associated internal logic for that channel is also powered down. A device reset (RESET sampled LOW) disables all output drivers.

**Note**. When a disabled channel (i.e., both outputs disabled) is re-enabled:

- data on the serial outputs may not meet all timing specifications for up to 250  $\mu s$

- the state of the phase-align buffer cannot be guaranteed, and a phase-align reset is required if the phase-align buffer is used

## **Device Configuration and Control Interface**

The CYV15G0203TB is highly configurable via the configuration interface. The configuration interface allows each channel to be configured independently. Table 2 on page 10 lists the configuration latches within the device including the initialization value of the latches upon the assertion of RESET. Table 3 on page 11 shows how the latches are mapped in the device. Each row in the Table 3 maps to a 4-bit latch bank. There are 6 such write-only latch banks. When WREN = 0, the logic value in the DATA[3:0] is latched to the latch bank specified by the values in ADDR[2:0]. The second column of Table 3 specifies the channels associated with the corresponding latch bank. For example, the first three latch banks (0,1 and 2) consist of configuration bits for channel A.

#### Latch Types

There are two types of latch banks: static (S) and dynamic (D). Each channel is configured by 2 static and 1 dynamic latch banks. The S type contain those settings that normally do not change for a given application, whereas the D type controls the settings that could change during the application's lifetime. The first and second rows of each channel (address numbers 0, 1, 5, and 6) are the static control latches. The third row of latches for each channel (address numbers 2 and 7) are the dynamic control latches. Address numbers 3 and 4 are internal test registers.

#### Static Latch Values

There are some latches in the table that have a static value (i.e. 1, 0, or X). The latches that have a '1' or '0' must be configured with their corresponding value each time that their associated latch bank is configured. The latches that have an 'X' are don't cares and can be configured with any value.

#### Table 2. Device Configuration and Control Latch Descriptions

| Name                 | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXCKSELA<br>TXCKSELB | <b>Transmit Clock Select</b> . The initialization value of the TXCKSELx latch = 1. TXCKSELx selects the clock source used to write data into the Transmit Input Register. When TXCKSELx = 1, the associated input register TXDx[9:0] is clocked by REFCLKx <sup>1</sup> . In this mode, the phase alignment buffer is bypassed. When TXCKSELx = 0, the associated TXCLKx <sup>1</sup> is used to clock in the input register TXDx[9:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXRATEA<br>TXRATEB   | <b>Transmit PLL Clock Rate Select</b> . The initialization value of the TXRATEx latch = 0. TXRATEx is used to select the clock multiplier for the Transmit PLL. When TXRATEx = 0, each transmit PLL multiples the associated REFCLKx± input by 10 to generate the serial bit-rate clock. When TXRATEx = 0, the TXCLKOx output clocks are full-rate clocks and follow the frequency and duty cycle of the associated REFCLKx± input. When TXRATEx = 1, each Transmit PLL multiplies the associated REFCLKx± input by 20 to generate the serial bit-rate clock. When TXRATEx = 1, the TXCLKOx output clocks are twice the frequency rate of the REFCLKx± input. When TXRATEx = 1, the TXCLKOx output clocks are twice the frequency rate of the REFCLKx± input. When TXCLKSELx = 1 and TXRATEx = 1, the Transmit Data Inputs are captured using both the rising and falling edges of REFCLKx. TXRATEx = 1 and SPDSELx = LOW, is an invalid state and this combination is reserved. |

| TXBISTA<br>TXBISTB   | <b>Transmit Bist Disabled</b> . The initialization value of the TXBISTx latch = 1. TXBISTx selects if the transmit BIST is disabled or enabled. When TXBISTx = 1, the transmit BIST function is disabled. When TXBISTx = 0, the transmit BIST function is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OE2A<br>OE2B         | Secondary Differential Serial Data Output Driver Enable. The initialization value of the OE2x latch = 0. OE2x selects if the OUT2x± secondary differential output drivers are enabled or disabled. When OE2x = 1, the associated serial data output driver is enabled allowing data to be transmitted from the transmit shifter. When OE2x = 0, the associated serial data output driver is disabled. When a driver is disabled via the configuration interface, it is internally powered down to reduce device power. If both serial drivers for a channel are in this disabled state, the associated internal logic for that channel is also powered down. A device reset (RESET sampled LOW) disables all output drivers.                                                                                                                                                                                                                                                     |

| OE1A<br>OE1B         | <b>Primary Differential Serial Data Output Driver Enable</b> . The initialization value of the OE1x latch = 0. OE1x selects if the OUT1x± primary differential output drivers are enabled or disabled. When OE1x = 1, the associated serial data output driver is enabled allowing data to be transmitted from the transmit shifter. When OE1x = 0, the associated serial data output driver is disabled. When a driver is disabled via the configuration interface, it is internally powered down to reduce device power. If both serial drivers for a channel are in this disabled state, the associated internal logic for that channel is also powered down. A device reset (RESET sampled LOW) disables all output drivers.                                                                                                                                                                                                                                                 |

| PABRSTA<br>PABRSTB   | <b>Transmit Clock Phase Alignment Buffer Reset</b> . The initialization value of the PABRSTx latch = 1. The PABRSTx is used to re-center the Transmit Phase Align Buffer. When the configuration latch PABRSTx is written as a 0, the phase of the TXCLKx input clock relative to its associated REFCLKx+/- is initialized. PABRST is an asynchronous input, but is sampled by each TXCLKx↑ to synchronize it to the internal clock domain. PABRSTx is a self clearing latch. This eliminates the requirement of writing a 1 to complete the initialization of the Phase Alignment Buffer.                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Device Configuration Strategy**

The following is a series of ordered events needed to load the configuration latches on a per channel basis:

- 1. Pulse RESET Low after device power-up. This operation resets both channels. Initialize the JTAG state machine to its reset state as detailed in the JTAG Support section.

- 2. Set the static latch banks for the target channel.

- 3. Set the dynamic bank of latches for the target channel. Enable the output drivers. [Required step.]

- 4. Reset the Phase Alignment Buffer for the target channel. [Optional if phase align buffer is bypassed.]

### JTAG Support

The CYV15G0203TB contains a JTAG port to allow system level diagnosis of device interconnect. Of the available JTAG modes, boundary scan, and bypass are supported. This capability is present only on the LVTTL inputs and outputs and the REFCLKx± clock input. The high-speed serial inputs and

outputs are not part of the JTAG test chain. To ensure valid device operation after power-up (including non-JTAG operation), the JTAG state machine should also be initialized to a reset state. This should be done in addition to the device reset (using RESET). The JTAG state machine can be initialized using TRST (asserting it LOW and de-asserting it or leaving it asserted), or by asserting TMS HIGH for at least 5 consecutive TCLK cycles. This is necessary in order to ensure that the JTAG controller does not enter any of the test modes after device power-up. In this JTAG reset state, the rest of the device will be in normal operation.

**Note**. The order of device reset (using RESET) and JTAG initialization does not matter.

#### **3-Level Select Inputs**

Each 3-Level select inputs reports as two bits in the scan register. These bits report the LOW, MID, and HIGH state of the associated input as 00, 10, and 11 respectively

### JTAG ID

The JTAG device ID for the CYV15G0203TB is '0C810069'x.

## Table 3. Device Control Latch Configuration Table

| ADDR         | Channel | Туре | DATA3   | DATA2 | DATA1    | DATA0   | Reset<br>Value |

|--------------|---------|------|---------|-------|----------|---------|----------------|

| 0<br>(000b)  | A       | S    | Х       | Х     | 0        | Х       | 1111           |

| 1<br>(001b)  | A       | S    | Х       | 0     | TXCKSELA | TXRATEA | 0110           |

| 2<br>(010b)  | A       | D    | TXBISTA | OE2A  | OE1A     | PABRSTA | 1001           |

| 9<br>(101b)  | В       | S    | Х       | Х     | 0        | Х       | 1111           |

| 10<br>(110b) | В       | S    | Х       | 0     | TXCKSELB | TXRATEB | 0110           |

| 11<br>(111b) | В       | D    | TXBISTB | OE2B  | OE1B     | PABRSTB | 1001           |

## **Maximum Ratings**

Above which the useful life may be impaired. User guidelines only, not tested

| Storage Temperature65°C to +150°C                                                 |

|-----------------------------------------------------------------------------------|

| Ambient Temperature with<br>Power Applied55°C to +125°C                           |

| Supply Voltage to Ground Potential0.5V to +3.8V                                   |

| DC Voltage Applied to LVTTL Outputs in High-Z State0.5V to V <sub>CC</sub> + 0.5V |

| Output Current into LVTTL Outputs (LOW)60 mA                                      |

| DC Input Voltage0.5V to V <sub>CC</sub> + 0.5V                                    |

## CYV15G0203TB DC Electrical Characteristics

Static Discharge Voltage.....> 2000 V (per MIL-STD-883, Method 3015)

Latch-up Current.....> 200 mA

### Power-up Requirements

The CYV15G0203TB requires one power-supply. The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

#### **Operating Range**

| R   | Range    | Ambient Temperature | V <sub>CC</sub> |

|-----|----------|---------------------|-----------------|

| Com | nmercial | 0°C to +70°C        | +3.3V ±5%       |

| Parameter                          | Description                                | Test Conditions                                               | Min.                   | Max.                   | Unit |

|------------------------------------|--------------------------------------------|---------------------------------------------------------------|------------------------|------------------------|------|

| LVTTL-com                          | patible Outputs                            |                                                               |                        | •                      |      |

| V <sub>OHT</sub>                   | Output HIGH Voltage                        | $I_{OH} = -4 \text{ mA}, V_{CC} = \text{Min}.$                | 2.4                    |                        | V    |

| V <sub>OLT</sub>                   | Output LOW Voltage                         | $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}.$                 |                        | 0.4                    | V    |

| I <sub>OST</sub>                   | Output Short Circuit Current               | V <sub>OUT</sub> = 0V <sup>[7]</sup> , V <sub>CC</sub> = 3.3V | -20                    | -100                   | mA   |

| I <sub>OZL</sub>                   | High-Z Output Leakage Current              | $V_{OUT} = 0V, V_{CC}$                                        | -20                    | 20                     | μA   |

| LVTTL-com                          | patible Inputs                             |                                                               |                        | •                      | .1   |

| V <sub>IHT</sub>                   | Input HIGH Voltage                         |                                                               | 2.0                    | V <sub>CC</sub> + 0.3  | V    |

| V <sub>ILT</sub>                   | Input LOW Voltage                          |                                                               | -0.5                   | 0.8                    | V    |

| I <sub>IHT</sub>                   | Input HIGH Current                         | REFCLKx Input, V <sub>IN</sub> = V <sub>CC</sub>              |                        | 1.5                    | mA   |

|                                    |                                            | Other Inputs, $V_{IN} = V_{CC}$                               |                        | +40                    | μA   |

| I <sub>ILT</sub>                   | Input LOW Current                          | REFCLKx Input, V <sub>IN</sub> = 0.0V                         |                        | -1.5                   | mA   |

|                                    |                                            | Other Inputs, V <sub>IN</sub> = 0.0V                          |                        | -40                    | μA   |

| I <sub>IHPDT</sub>                 | Input HIGH Current with internal pull-down | $V_{IN} = V_{CC}$                                             |                        | +200                   | μA   |

| I <sub>ILPUT</sub>                 | Input LOW Current with internal pull-up    | $V_{IN} = 0.0V$                                               |                        | -200                   | μA   |

| LVDIFF Inp                         | uts: REFCLKx±                              |                                                               |                        | •                      |      |

| V <sub>DIFF</sub> <sup>[8]</sup>   | Input Differential Voltage                 |                                                               | 400                    | V <sub>CC</sub>        | mV   |

| V <sub>IHHP</sub>                  | Highest Input HIGH Voltage                 |                                                               | 1.2                    | V <sub>CC</sub>        | V    |

| V <sub>ILLP</sub>                  | Lowest Input LOW voltage                   |                                                               | 0.0                    | V <sub>CC</sub> /2     | V    |

| V <sub>COMREF</sub> <sup>[9]</sup> | Common Mode Range                          |                                                               | 1.0                    | V <sub>CC</sub> – 1.2V | V    |

| 3-Level Inp                        | uts                                        |                                                               |                        | 1                      |      |

| V <sub>IHH</sub>                   | Three-Level Input HIGH Voltage             | Min. $\leq$ V <sub>CC</sub> $\leq$ Max.                       | 0.87 * V <sub>CC</sub> | V <sub>CC</sub>        | V    |

| V <sub>IMM</sub>                   | Three-Level Input MID Voltage              | $Min. \leq V_{CC} \leq Max.$                                  | 0.47 * V <sub>CC</sub> | 0.53 * V <sub>CC</sub> | V    |

| V <sub>ILL</sub>                   | Three-Level Input LOW Voltage              | $Min. \leq V_{CC} \leq Max.$                                  | 0.0                    | 0.13 * V <sub>CC</sub> | V    |

| I <sub>IHH</sub>                   | Input HIGH Current                         | $V_{IN} = V_{CC}$                                             |                        | 200                    | μA   |

| I <sub>IMM</sub>                   | Input MID current                          | $V_{IN} = V_{CC}/2$                                           | -50                    | 50                     | μA   |

| I <sub>ILL</sub>                   | Input LOW current                          | V <sub>IN</sub> = GND                                         |                        | -200                   | μA   |

| Differential                       | CML Serial Outputs: OUTA1±, OUTA2±, OU     | JTB1±, OUTB2±, OUTC1±, OU                                     | rc2±, outd1±           | , OUTD2±               |      |

| V <sub>OHC</sub>                   | Output HIGH Voltage                        | $100\Omega$ differential load                                 | $V_{CC} - 0.5$         | V <sub>CC</sub> -0.2   | V    |

|                                    | (V <sub>cc</sub> Referenced)               | 150 $\Omega$ differential load                                | V <sub>CC</sub> – 0.5  | V <sub>CC</sub> – 0.2  | V    |

Notes

7. Tested one output at a time, output shorted for less than one second, less than 10% duty cycle.

8. This is the minimum difference in voltage between the true and complement inputs required to ensure detection of a logic-1 or logic-0. A logic-1 exists when the true (1) input is more positive than true (1) input is more positive than true (1) input is

true (+) input is more positive than the complement (-) input. A logic-0 exists when the complement (-) input is more positive than the complement (-) input.

The common mode range defines the allowable range of REFCLKx+ and REFCLKx- when REFCLKx+ = REFCLKx-. This marks the zero-crossing between the algorithm of the algorithm of the algorithm of the algorithm of the algorithm.

the true and complement inputs as the signal switches between a logic-1 and a logic-0.

### CYV15G0203TB DC Electrical Characteristics (continued)

| Parameter                          | Description                  | Test Conditions                 | Min.                  | Max.                  | Unit |

|------------------------------------|------------------------------|---------------------------------|-----------------------|-----------------------|------|

| V <sub>OLC</sub>                   | Output LOW Voltage           | $100\Omega$ differential load   | V <sub>CC</sub> – 1.4 | V <sub>CC</sub> – 0.7 | V    |

|                                    | (V <sub>CC</sub> Referenced) | $150\Omega$ differential load   | V <sub>CC</sub> – 1.4 | V <sub>CC</sub> – 0.7 | V    |

| V <sub>ODIF</sub>                  | Output Differential Voltage  | $100\Omega$ differential load   | 450                   | 900                   | mV   |

|                                    | (OUT+) – (OUT–)              | 150 $\Omega$ differential load  | 560                   | 1000                  | mV   |

| Power Sup                          | ply                          |                                 | Тур.                  | Max.                  |      |

| I <sub>CC</sub> <sup>[10,11]</sup> | Max Power Supply Current     | REFCLKx = Commercial<br>MAX     | 435                   | 530                   | mA   |

| I <sub>CC</sub> <sup>[10,11]</sup> | Typical Power Supply Current | REFCLKx = Commercial<br>125 MHz | 425                   | 520                   | mA   |

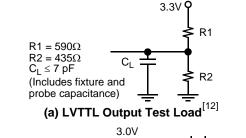

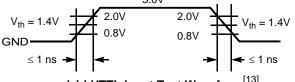

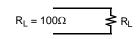

### AC Test Loads and Waveforms

(c) LVTTL Input Test Waveform<sup>[13]</sup>

(Includes fixture and probe capacitance)

(b) CML Output Test Load<sup>[12]</sup>

(d) CML/LVPECL Input Test Waveform

# CYV15G0203TB AC Electrical Characteristics

| Parameter                                                                         | Description                                                   | Min. | Max.  | Unit |  |  |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------|------|-------|------|--|--|--|--|

| CYV15G0203TB Transmitter LVTTL Switching Characteristics Over the Operating Range |                                                               |      |       |      |  |  |  |  |

| f <sub>TS</sub>                                                                   | TXCLKx Clock Cycle Frequency                                  | 19.5 | 150   | MHz  |  |  |  |  |

| t <sub>TXCLK</sub>                                                                | TXCLKx Period=1/f <sub>TS</sub>                               | 6.66 | 51.28 | ns   |  |  |  |  |

| t <sub>TXCLKH</sub> <sup>[14]</sup>                                               | TXCLKx HIGH Time                                              | 2.2  |       | ns   |  |  |  |  |

| t <sub>TXCLKL</sub> <sup>[14]</sup>                                               | TXCLKx LOW Time                                               | 2.2  |       | ns   |  |  |  |  |

| t <sub>TXCLKR</sub> [14, 15, 16, 7                                                | <sup>[7]</sup> TXCLKx Rise Time                               | 0.2  | 1.7   | ns   |  |  |  |  |

| t <sub>TXCLKF</sub> [14, 15, 16, 1                                                | 7) TXCLKx Fall Time                                           | 0.2  | 1.7   | ns   |  |  |  |  |

| t <sub>TXDS</sub>                                                                 | Transmit Data Set-up Time to TXCLKx $\uparrow$ (TXCKSELx = 0) | 2.2  |       | ns   |  |  |  |  |

| t <sub>TXDH</sub>                                                                 | Transmit Data Hold Time from TXCLKx $\uparrow$ (TXCKSELx = 0) | 1.0  |       | ns   |  |  |  |  |

| f <sub>TOS</sub>                                                                  | TXCLKOx Clock Frequency = 1x or 2x REFCLKx Frequency          | 19.5 | 150   | MHz  |  |  |  |  |

| t <sub>TXCLKO</sub>                                                               | TXCLKOx Period = 1/f <sub>TOS</sub>                           | 6.66 | 51.28 | ns   |  |  |  |  |

| t <sub>TXCLKOD</sub>                                                              | TXCLKO Duty Cycle centered at 60% HIGH time                   | -1.9 | 0     | ns   |  |  |  |  |

#### Notes

Maximum I<sub>CC</sub> is measured with V<sub>CC</sub> = MAX, T<sub>A</sub> = 25°C, with both channels and Serial Line Drivers enabled, sending a continuous alternating 01 pattern, and outputs unloaded.

Typical I<sub>CC</sub> is measured under similar conditions except with V<sub>CC</sub> = 3.3V, T<sub>A</sub> = 25°C, with both channels enabled and one Serial Line Driver per channel sending a continuous alternating 01 pattern. The redundant outputs on each channel are powered down.

12. Cypress uses constant current (ATE) load configurations and forcing functions. This figure is for reference only. 13. The LVTTL switching threshold is 1.4V. All timing references are made relative to where the signal edges cross the threshold voltage.

14. Tested initially and after any design or process changes that may affect these parameters, but not 100% tested.

15. The ratio of rise time to falling time must not vary by greater than 2:1.

16. For a given operating frequency, neither rise or fall specification can be greater than 20% of the clock-cycle period or the data sheet maximum time.